按关键词阅读: 算法 半导体

【嘉勤点评】芯和半导体的封装专利 , 通过较多的运用二维网格生成算法 , 网格生成速度更快 , 计算复杂度比三维网格算法要低很多 , 且相对于直接生成三维网络 , 生成的网格质量会有保障 。

【半导体|【专利解密】芯和半导体致力解决先进封装挑战】集微网消息 , 近日国内EDA、滤波器行业的领军企业芯和半导体的年度用户大会XTUG正式召开 。 芯和半导体技术专家就2.5D/3D异构集成对电磁仿真的挑战和解决方案做了详细介绍 。

随着PCB高速信号设计越发普遍 , 电子电路的设计也面临信号完整性、电源完整性、热、电磁兼容等问题挑战 。 在设计中引入仿真验证手段 , 将大大提升产品开发效率 , 设计正确性 , 实现产品快速推向市场 。 在现有仿真技术中 , 仿真网格一般都是四面体网格 。 四面体网格虽然是一种成熟的网格划分技术 , 但是面对PCB板的特殊情况 , 存在一些问题:前处理已经成为了仿真的效率瓶颈 , 需要较多的人工干预 , 网格质量较差等等 。

为此 , 芯和半导体于2020年12月7日申请了一项名为“一种应用于封装的分层扫掠网格划分方法”的发明专利(申请号: 202011416627.7) , 申请人为芯和半导体科技(上海)有限公司 。

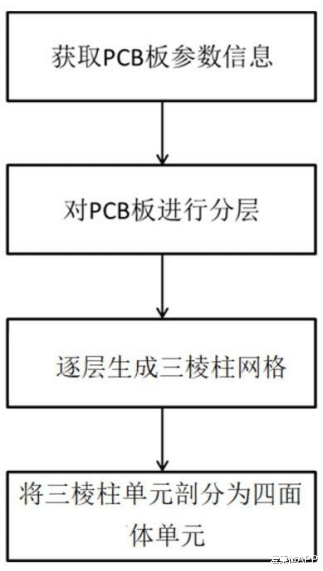

图1 分层扫掠网格划分方法流程示意图

图1为本发明应用于封装的分层扫掠网格划分方法流程示意图 , 获取PCB板的参数信息并对PCB板进行分层 , 从上而下对每层进行三棱柱网格划分 , 剖分每个三棱柱单元为3个四面体单元 , 即得三棱柱网络 。

该方法包括如下步骤:首先 , PCB板分层 , 按照PCB板的几何信息进行分层(S100);然后 , 对分层后的每一层的上表面和侧面进行平面网格划分 , 并将上表面划分的平面网格投影到该层的下表面(S200);接着 , 将上下表面对应的网格点进行连接并与侧面层相交 , 相交后生成的中间点进行连接即得该层三棱柱网格(S300);最后、依次将所有层的三棱柱网格进行组合 , 即得PCB板整体的三棱柱网格(S400) 。

步骤S100中分层的原则为根据材质的不同进行分层 , 由于PCB板由不同材质的材料分层组合而成 , 因此根据材质分层可以准确便捷的进行划分 。 步骤S200中对分层后的每一层的上表面和侧面进行平面网格划分 , 并将上表面划分的平面网格投影到该层的下表面 , 这里的网格尺寸可以为预设值或者由用户指定 , 也可以使用默认尺寸 , 由于最终需要生成四面体网格单元 , 所以在上表面生成三角形网格单元 , 而由于侧面需要保证网格结构的一致性 , 所以在侧面生成四边形网格单元 。 其中侧面进行平面网格划分时只划分四边形网络 。

简而言之 , 芯和半导体的封装专利 , 通过较多的运用二维网格生成算法 , 网格生成速度更快 , 计算复杂度比三维网格算法要低很多 , 且相对于直接生成三维网络 , 生成的网格质量会有保障 。

芯和半导体是国产EDA行业的领军企业 , 提供覆盖IC、封装到系统的全产业链仿真EDA解决方案 , 致力于赋能和加速新一代高速高频智能电子产品的设计 。 随着EDA工具在半导体先进工艺节点和先进封装上不断得到验证 , 芯和也将为用户提供更快更高效的产品方案 。

(校对/holly)

稿源:(未知)

【傻大方】网址:/c/1130ab062021.html

标题:半导体|【专利解密】芯和半导体致力解决先进封装挑战