随着收集、传送和存储的数据越来越多 , 模拟信号处理器件的性能也在不断扩大极限 , 有些甚至达到每秒千兆采样 。 由于创新的步伐从未放缓 , 下一代电子解决方案将使解决方案体积进一步缩少 , 电源效率持续提高 , 并对噪声性能提出更高的要求 。

我们可能认为应当最大限度地减少或隔离各电源域(模拟、数字、串行数字和数字输入输出(I/O))中产生的噪声 , 以实现出色的动态性能 , 但追求绝对最小噪声可能会使研究的收益递减 。 设计人员如何实现噪声与性能的最优配置?

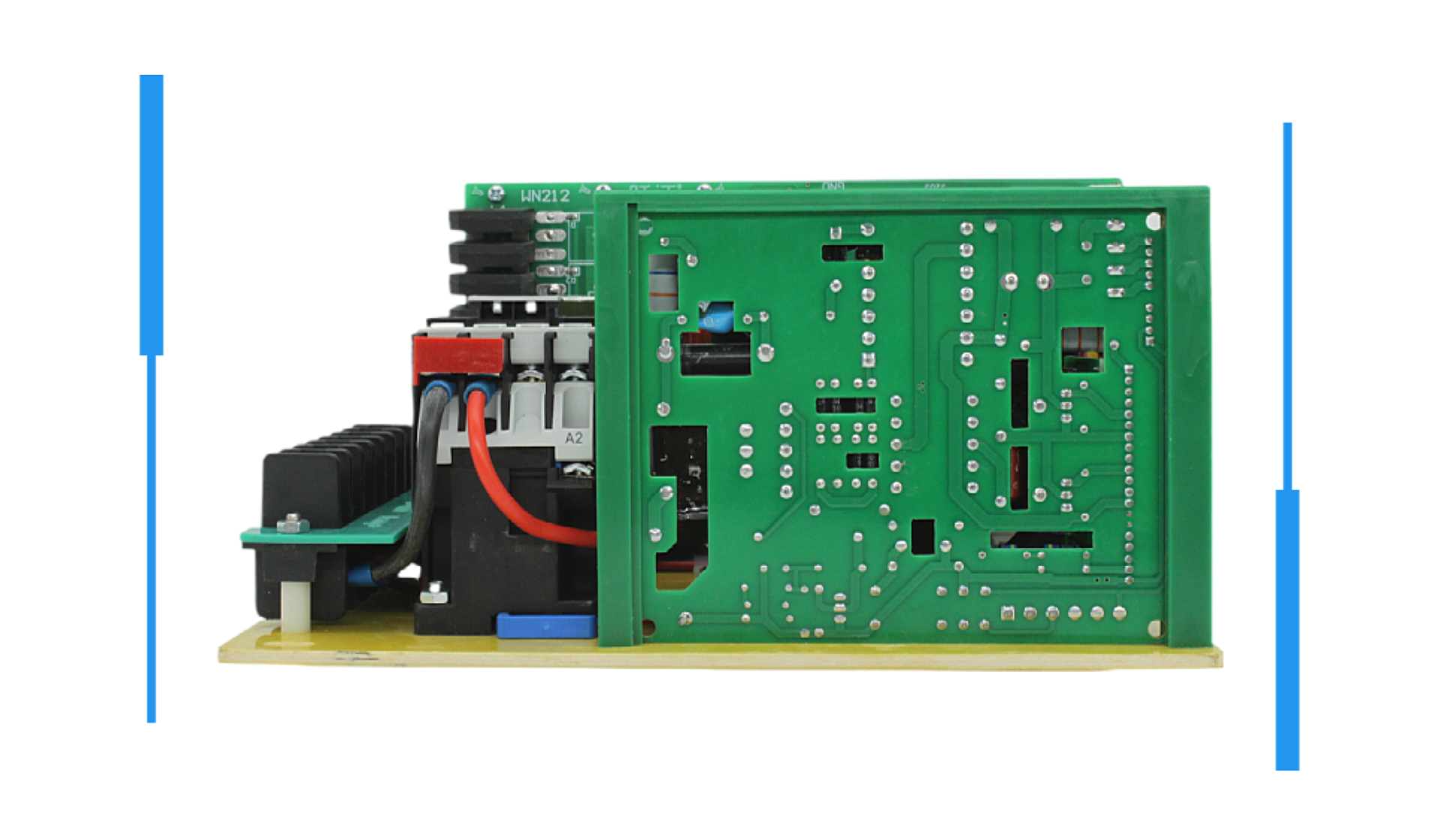

跃迁自主研发生产电源(接受个性化定制)

首先要量化器件的灵敏度 , 使电源频谱输出与该电源域要求匹配 。 通过避免过度设计来节约设计时间 , 对设计会有很大的帮助 。

电源优化的第一步是研究分析模拟信号处理器件对电源噪声的真正灵敏度 。 其中包括了解电源噪声对关键动态性能规格的影响 , 以及电源噪声灵敏度的表征 — 即 , 电源调制比(PSMR)和电源抑制比(PSRR) 。 PSMR和PSRR表明是否具有良好的电源抑制特性 , 但仅凭它们并不足以确定纹波应有多低 。 只有确定与电源频谱输出相匹配的阈值才可能实现优化电源系统设计 。 如果确保电源噪声低于其最大规格值 , 则优化电源不会降低每个模拟信号处理器件的动态性能 。

电源噪声可耦合到任何模拟信号处理系统的载波信号中 。 电源噪声的影响取决于其相对于频域中载波信号的强度 。 一种测量方法是SFDR , 它代表能与大干扰信号区分开来的最小信号 — 具体来讲 , 就是载波信号的幅度与最高杂散信号幅度的比值 。

对于模拟信号处理器件 , 通过时钟电源电压耦合到器件时钟中的电压噪声会产生相位噪声 , 进而影响内部本振(LO)的频率稳定性 。 这扩大了频谱中LO频率的范围 , 增加了与载波相对应的偏移频率下的功率密度 , 从而增加了相位噪声 。

备用电源添加一个低通滤波器以抑制高于1 MHz的噪声 , 添加一个ADP1764低压差(LDO)后置稳压器以减少整体本底噪声 , 特别是低于10 kHz的噪声(主要是SSFM产生的噪声) 。 由于额外滤波 , 整体电源噪声获得改善 , 从而增强了10 kHz偏移频率以下的相位噪声性能 。

PSRR表示器件在一定频率范围内衰减电源引脚噪声的能力 。 通常 , 有两种类型的PSRR:静态(直流)PSRR和动态(交流)PSRR 。 直流PSRR用于衡量直流电源电压变化引起的输出失调变化 。 这一点几乎无需关注 , 因为电源系统应该会为负载提供稳定调节的直流电压 。 另一方面 , 交流PSRR表示器件在一定频率范围内抑制直流电源中交流信号的能力 。

交流PSRR通过在器件的电源引脚注入正弦波信号 , 并观察在注入频率下出现在数据转换器/收发器输出频谱本底噪声上的误差杂散来确定 。 交流PSRR定义为测得的注入信号幅度与输出频谱上相应的误差杂散幅度之比 。

PSMR对模拟信号处理器件的影响与PSRR不同 。 PSMR表示使用RF载波信号进行调制时 , 器件对电源噪声的灵敏度 。 这种效应可以看作是施加于器件的载波频率周围的调制杂散 , 表现为载波边带 。

电源调制通过使用线路注入器/耦合电路将输入纹波信号与干净的直流电压相结合来实现 。 电源纹波作为正弦波信号从信号发生器注入电源引脚 。 调制到RF载波的正弦波产生边带杂散 , 其偏移频率等于正弦波频率 。 杂散水平受正弦波幅度和器件灵敏度的影响 。 简化的PSMR测试设置与PSRR的相同 , 但输出主要显示载波频率及其边带杂散 。 PSMR定义为电源注入纹波幅度与载波周围调制边带杂散幅度的比值 。

PSMR可与受电器件的基准阈值相结合 , 用于确定模拟信号处理器件的每个电源域的最大允许电压纹波 。 基准阈值本身可以是几个值之一 , 代表器件可容忍而不会显著影响其动态性能的允许杂散电平(由电源纹波引起) 。 此杂散电平可以是无杂散动态范围(SFDR) , 最低有效位(LSB)的百分比或输出频谱本底噪声 。

高速模拟信号处理器件出色的动态性能很容易被电源噪声削弱 。 为了避免系统性能下降 , 必须充分了解信号链对电源噪声的灵敏度 。 这可通过设定最大允许纹波来确定 , 最大允许纹波对于配电网络(PDN)设计至关重要 。 知道最大允许纹波阈值后 , 就可以采用各种方法来设计优化电源 。 如果最大允许纹波具有良好的裕度 , 则PDN不会降低高速模拟信号处理器件的动态性能 。

- 游戏手机|电源芯片DC-DC转换器参数

- Linux|PC全模组电源与半模组电源的区别?什么是模组电源定制线?

- 显卡|迎接40系显卡,微星A1000G金牌全模组电源装机体验

- 白金|小而美 满血旗舰,艾湃电竞SFX 白金系列电源正式上市

- |热水器不用时要不要拔电源?看完才知道,原来我一直做错

- 移动电源|“次世代游戏旗舰” iQOO Neo6 将携44W闪充移动电源共同亮相

- fx|超频三ITX箱电组合-蜂鸟I100 PRO +矾星-FX500电源

- 移动电源|iQOO在中国正式推出新款44W闪充移动电源

- 机箱|最便宜的白色SFX电源!ITX爱好者狂喜!超频三 500W SFX

- |为什么要买80PLUS认证电源?装机如何选电源,这篇文章告诉你