|说人话系列:英特尔酷睿12代详解(4): 摩尔定律之殇

文章图片

文章图片

文章图片

文章图片

火龙888镇楼

众所周知 , 骁龙888系列是个笑话 。 搭载骁龙888的安卓手机 , 发热大 , 耗电快 , 性能峰值上不去 , 结合在一起用一个词概括:废物 。 当然这不是高通第一次如此头铁了 。 上一次这么热 , 是7年前的骁龙810 , 因为过热造成体验降级 , 直接把索尼LG等一堆高价日韩系手机干没了市场份额 。 而上上次这么热 , 是13年前 , 超频到800MHZ的高通MSM7225系列 , 直接让还能继续战斗1年的windowsMobile6.5系统手机全线提前市场消失 。 所以说 , 高通是有原罪的(确信) 。

那问题来了 , 为何骁龙888采用的三星5nm工艺 , 包括骁龙810采用的台积电20nm工艺 , MSM7225系列采用的第一代台积电65nm工艺 , 都这么热?芯片制程不是越小越好嘛?

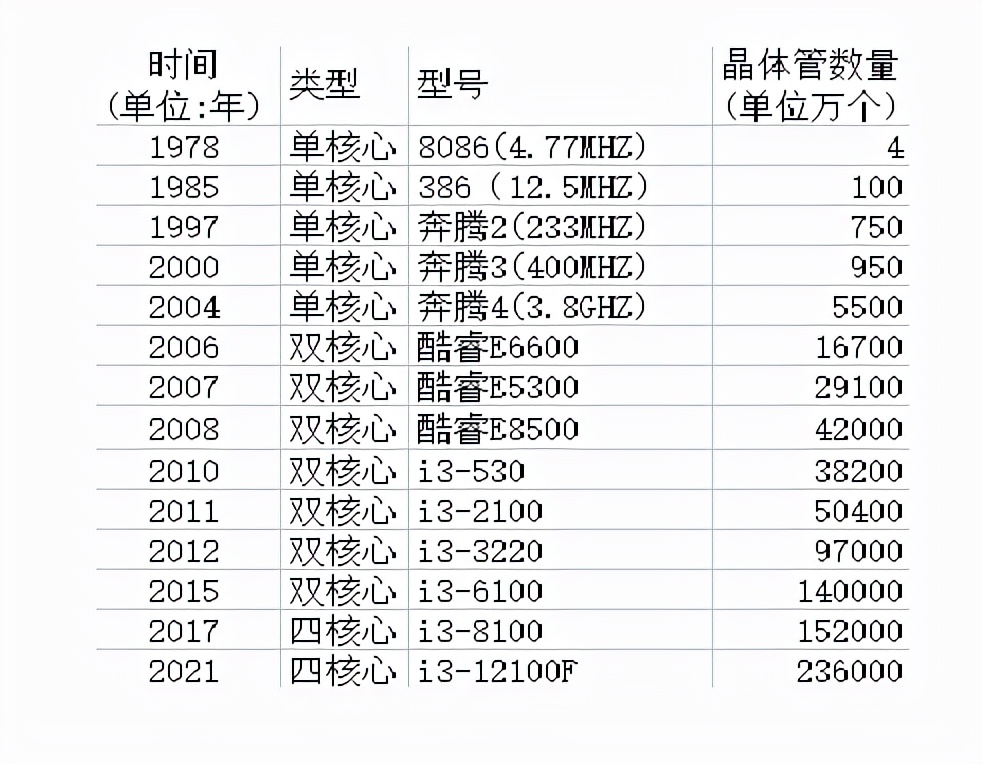

摩尔规律

大家都知道一个摩尔定律 , 其实就是戈登摩尔总结的半导体发展规律 , 版本很多 , 但是显然英特尔那边的说法是 , 每24个月 , 半导体晶体管规模跟性能要翻一倍 。 结合本系列前几篇的说法 , 确实如此嘛 , 从1960年代开始 , 芯片晶体管跟频率都在不断增加 。 半导体工艺也越缩越小 , 确实如此 。

60年来晶体管翻了6万倍

晶体管结构在物理层面足够大的时候 , 不断缩小是可行的 。 但是如果晶体管达到一个非常小的规模的话 , 比如达到一个很小的程度 , 小到不能阻止电子漏出通道的程度 , 那这个工艺本身就会发热漏电耗电严重了 。 而这个节点 , 并不是眼前的什么1nm之类“先进工艺” , 而是20世纪初的65nm工艺 。 从1996到2005年10年时间 , 65nm工艺困扰了人类很久 , 始终无法低成本量产65nm芯片 , 无论IBM , 英特尔还是AMD 。 而当时的大量芯片 , 都卡在90nm工艺接近10年 , 比如ARM789全线处理器 , 游戏机 , 甚至包括英特尔自己的PXA移动处理器系列 。 有个常识就是 , 65nm并不比90nm工艺更省电 , 甚至静态功耗还要多 , 这就是高通MSM72XX系如此拉垮的原因 。 这样可以快进到芯片制造现在面对的更大的一个问题 , 量子隧穿效应下2nm能不能实现都是疑问 。

某百科的原话:隧穿电子是指发生隧穿的电子(废话) 。 隧穿效应是一种量子特性 , 是电子等微观粒子能够穿过它们本来无法通过的“墙壁”的现象 。 这就说的很明白了 , 当“墙壁”的“缝隙”足够电子乱窜 , 特别是“墙壁”的“砖头”足够小的时候 , 那墙壁就失去了作用嘛 。 65nm时代就有低配版的这个问题出现 , 解决时间是10年 。

量子隧穿

以2000年前后来说 , 传统芯片制造模式 , 是以IBM技术指导路线加整个日本工艺技术生产经验定义的 。 整个芯片内部电路排布 , 从头到尾都是平面铺开设计的 。 这也是传统意义上的电路布局嘛 。 特别是尼康佳能的光刻设备阵列 , 也是这个思路一路延伸 。 但是如果芯片缩小到了一个程度 , 电子泄漏 , 电路通电会收到互联线的磁场干扰 , 这会让频率上不去 。 这就是串扰(crosstalk) , 以及噪声(noise) , 这也是当时英特尔宣布不玩频率战争的一个理由 。

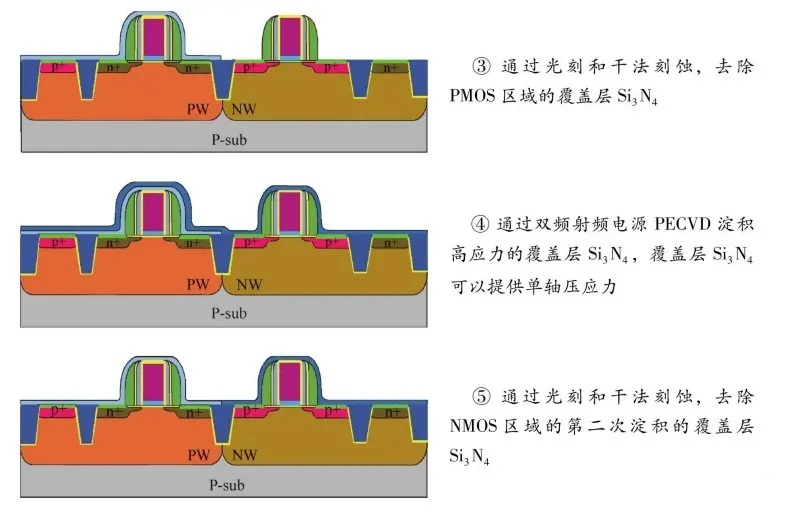

如何解决呢?英特尔引入了应变硅+HKMG技术 。 而AMD引入了掺铜绝缘硅技术 , 大大降低了芯片内部漏电率跟受到的电磁影响 , 再加上FPGA公司都在推行可编程功耗(Programmable Power)的方法 , 这一套软件硬件同步进步 , 加上标准改变新的供应链体系改变 , 行成了完善组合拳 , 从而理论上能把半导体制造工艺一路推进到32nm制程 。 而比较著名的代工厂台积电也学习AMD的铜互联方案 , 终于在2007年搞定了65nm工艺 。 这也有了别的问题 , 日美半导体标准决战 , 最终欧美技术胜利 , 曾经风头无两的日厂从此沦落 , 截至现在都在液晶硬盘领域苟延残喘 。

上了书本的应变硅技术

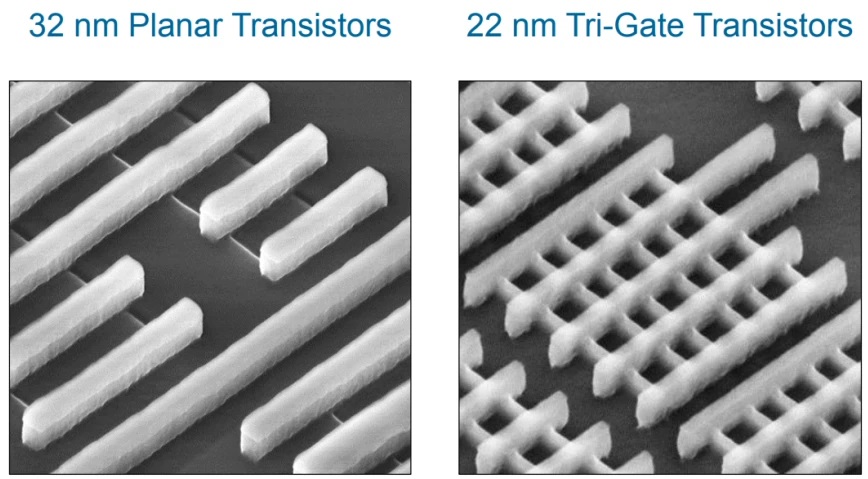

既然解决了眼前的问题 , 那就在平面晶体管制造上继续快进 。 时间来到了2010年 , 如何进行32nm下一代的设计 , 英特尔花了很多心思 。 实际上 , 平面铺设晶体管在10年前就早已提前宣布了走到了尽头 , 不过这一天总会来的 。 英特尔祭出了大杀器——3D晶体管(其实就是FinFET结构啦) 。

- 安卓|安卓将对懒惰的开发者说“不”,这会是件大好事

- 滴滴出行|滴滴还能逆袭?柳青、程维再添动作,官媒说得很对

- 曲面屏|进入倒计时!鸿蒙OS 3.0即将“内测”,Mate 50系列首发登场!

- AMD|OPPO新机刚遭曝光就被官方辟谣,但Ace系列却传出重启消息!

- 顺丰速运|刘强东说出了本质,顺丰拒绝菜鸟是必然的

- realme|低配版都拥有8+256G内存!realme真我V系列新机曝光,型号V23

- 苹果|毫不逊色于苹果系列,国产5G旗舰机器,这两款性价比极高

- 天玑9000|vivo X80系列曝光:有望本月发布!搭载最强天玑9000性能爆表!

- |都在说直播要不得,中国不适合直播,直播让很多行业萧条,很多人失业

- 带货|7200W粉小杨哥再陷争议?背后团队首曝,网友:说好的无团队呢?